以下列表概述了数字 IC 设计流程中的步骤,包括子步骤:

高级系统设计

-

设计分区

-

入门 Verilog 行为建模

-

模拟/功能验证

-

集成与验证

逻辑综合

-

寄存器传输级 (RTL) 转换为网表

-

设计划分为物理块

-

时序裕量和时序约束

-

RTL和门级网表验证

-

静态时序分析

平面规划

合成

-

时序约束和优化

-

静态时序分析

-

更新展示位置

-

更新电源和时钟规划

块级布局

IC 级布局

-

所有模块的IC集成

-

单元格放置

-

扫描链/时钟树插入

-

信元路由

-

物理和电气设计规则检查 (DRC)

-

布局与原理图 (LVS)

-

寄生提取

-

布局后时序验证

-

GDSII 创建

-

流片

https://www.allaboutcircuits.com/technical-articles/what-is-digital-ic-design/

https://www.allaboutcircuits.com/technical-articles/what-is-analog-ic-design/

https://www.allaboutcircuits.com/technical-articles/what-is-rf-integrated-circuit-design/

目录

数字

IC

及???

数字

IC

岗位

IC

设计

的主要职责如下:

IC

验证的主要职责如下:怎样学习

数字

IC

相关知识Verilog推荐资料和书籍:System Verilog推荐书籍:UVM推荐资料和书籍:

数字

IC

及???

数字

IC

近些年热度越来越高,在2020年,我国将集成电路这一专业设置为一级学科,这足以看出我国对这方面的重视;并且随着国外的

芯片

限制,国内加大了对集成电路的投资,着力发展

芯片

产业,这方面人才的需求也在不断扩大。很多同学都萌生了转行

数字

IC

的想法,其中也包括我。还在纠结自己方向以及想了解

IC

设计

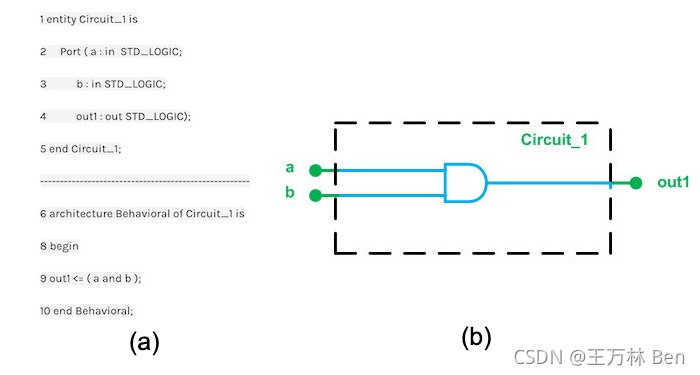

是一个很复杂漫长的过程,笔者以下图进行总结,其中后端总结的很模糊,后续了解学习后再进行补充。笔者会根据自己的理解,一步步的分享自己理解的

设计

流程。其中难免有问题错误,望同学老师指出,感谢!

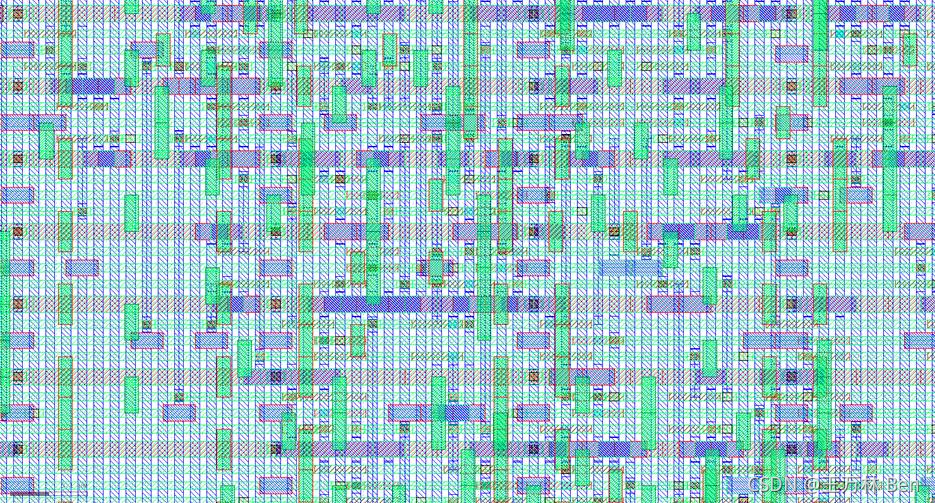

首先下面这张图是笔者总结的

数字

IC

设计

流程图。从

设计

需求到Tape-Out。下面会详细说明这张图的内容,后续也会持续修改更正。

设计

需求

首先是需求

设计

,一般的

设计

无非就是两个来源,一个是新的项目,需求来自市场,另外一个来自与继承项目的迭代。这两个均有产品经理(

IC

产品工程师)进行收集汇总,然后以给出

设计

需.

数字

IC

设计

流程写在前面

数字

IC

设计

的流程1. 项目需求2. 系统

设计

3. 前端

设计

4. 后端

设计

最后的总结

时隔一年,我已经找完工作,正式转行

数字

IC

。对于自己的未来,我很清楚,从事

数字

IC

设计

这个职业,对于我来说,即是机遇也是挑战。古人云,千里之行,始于足下。不积跬步无以至千里,不积小流无以成江海。借着最近一段时间写毕业论文的闲暇时光,我想,我也应该开始梳理自己的知识体系,夯实自己

数字

IC

设计

的基本功。

数字

IC

设计

的流程

都说FPGA与

数字

IC

很相似,但是实际上,

数字

IC

主要是对于AS

IC

设

5)一致性验证(Formality)Synopsys的Formality。3)逻辑综合(DC)Synopsys的Design Compiler。3)时钟树综合 Synopsys的Phys

ic

al Compiler。4)静态时序分析(PT)Synopsys的Prime Time。1)DFT Synopsys的DFT Compiler。6)版图物理验证 Synopsys的Hercules。2)布局规划 Synopsys的Astro。4)布线 Synopsys的Astro。2)功能仿真(VCS+Verdi)

集成电路(Integrated Circuit,

IC

)又称

芯片

,是现代信息社会的基石,它承载了信息时代的灵魂,是现代技术发展的精华结晶,所有现代的电子设备都必须依赖于

芯片

才能发挥出完全功效。集成电路现在已经演变为一个完整且独立的设备形态,单个

芯片

就可以完成一个传统的设备系统功能,达到真正的System on Chip(SoC)。

IC

设计

实现方式有很多种,模拟

IC

的实现方式主要包括:全定制与宏单元/IP。SoC的实现方式主要是依靠CPU/DSP/MCU/ASSP作为主控单元(用于系统处理控制)并搭配其它IP构成片上系统

芯片

。而

数字

IC

实现发主要方式有以下几种。