verilog

是什么

Verilog一般指Verilog HDL。Verilog HDL是一种

硬件

描述语言(HDL:Hardware Description Language),以文本形式来描述数字系统硬件的结构和行为的语言,用它可以表示逻辑电路图、逻辑表达式,还可以表示数字逻辑系统所完成的逻辑功能。 Verilog HDL和VHDL是世界上最流行的两种硬件描述语言,都是在20世纪80年代中期开发出来的。前者由Gateway Design Automation

公司

(该公司于1989年被

Cadence

公司收购)开发。两种HDL均为IEEE标准。

Verilog发展历史

1、1981年Gateway Automation(GDA)硬件描述语言公司成立。

2、1983年该公司的Philip Mo

or

by首创了Verilog HDL,Moorby后来成为Verrlog HDL-XL的主要设计者和Cadence公司的第一合伙人。

3、1984-1985年Moorby设计出第一个关于Verilog HDL的

仿真器

。

4、1986年Moorby对Verilog HDL的发展又做出另一个巨大的贡献,提出了用于快速门级

仿真

的XL

算法

。

5、随着Verilog HDL-XL的成功,Verilog HDL语言得到迅速发展。

6、1987年Synonsys公司开始使用Verilog HDL行为语言作为综合工具的输入。

7、1989年Cadence公司收购了Gateway公司,Verilog HDL成为Cadence公司的私有财产。

8、1990年初Cadence公司把Verilog HDL和Verilog HDL-XL分开,并公开发布了Verilog HDL.随后成立的OVI(Open Verilog HDL Interna

ti

onal)组织负责Verilog HDL的发展,OVI由Verilog HDL的使用和CAE供应商组成,制定标准。

9、1993年,几乎所有

ASIC

厂商

都开始支持Verilog HDL,并且认为Verilog HDL-XL是最好的仿真器。同时,OVI推出2.0版本的Verilong HDL规范,IEEE接收将OVI的Verilog HDL2.0作为IEEE标准的提案。

10、1995年12月,IEEE制定了Verilog HDL的标准IEEE1364-1995.

任何新生事物的产生都有它的历史沿革,早期的硬件描述语言是以一种高级语言为基础,加上一些特殊的约定而产生的,目的是为了实现RTL级仿真,用以验证设计的正确性,而不必像在传统的手工设计过程中那样,必须等到完成样机后才能进行实测和调试。

verilog的特征

1、采用verilog HDL 进行

电路设计

的最大优点是设计与工艺无关系,这使得设计在进行电路设计时可以不必过多考虑工艺实现时的具体细节,只需要根据系统设计的要求施加不同的约束条件,即可设计出实际电路。

2、能够在每个抽象层次的描述上对设计进行仿真验证,及时发现可能存在的设计错误,缩短设计周期,并保证整个设计过程的正确性;

3、能够在不同的抽象层次上,如系统级、行为级、RTL (RegisterTransfer Level) 级、门级和开关级,对设计系统进行精确而简练的描述。

Verilog逻辑门级描述

逻辑门级描述的抽象级别较低,仅次于

晶体管

级。实际的硬件电路往往都是以逻辑门级网表作为基础构建的,而设计人员常常会在进行更高抽象级别的设计。尽管如此,逻辑门级的设计还是更接近真实电路形式。Verilog提供了一系列逻辑门原语(Primitive)供用户使用。例如,非(not)、与门(and)、或门(or)、与非门(nand)、或非(nor)、异或(xor)、同或(xnor)。逻辑门原语和模块类似,可以通过实例引用的方式使用。

Verilog晶体管级描述

Verilog能够在低抽象级别对电路进行描述,是它的一个重要特点。Verilog中提供了多种晶体管级(也称开关级)元件类型,包括N型金属氧化物

半导体

场效应管(关键字为nmos)、P型金属氧化物半导体场效应管(关键字为pmos)、互补式金属氧化物半导体(关键字为cmos)、带阻抗的互补式金属氧化物半导体(关键字为rcmos)、

电源

单元(关键字为supply1)、接地单元(关键字为supply0)等。所有的晶体管都可以设置延迟属性。设计人员可以利用这些低抽象级元件构建所需要的逻辑门或直接构成其他高级组件。

verilog的用途

Verilog HDL就是在用途最广泛的

C语言

的基础上发展起来的一种硬件描述语言,它是由GDA(Gateway Design Automation)公司的PhilMoorby在1983年末首创的,最初只设计了一个仿真与验证工具,之后又陆续开发了相关的故障

模拟

与时序分析工具。1985年Moorby推出它的第三个商用仿真器Verilog-XL,获得了巨大的成功,从而使得Verilog HDL迅速得到推广应用。1989年CADENCE公司收购了GDA公司,使得VerilogHDL成为了该公司的独家专利。1990年CADENCE公司公开发表了Verilog HDL,并成立LVI组织以促进Verilog HDL成为IEEE标准,即IEEE Standard 1364-1995.

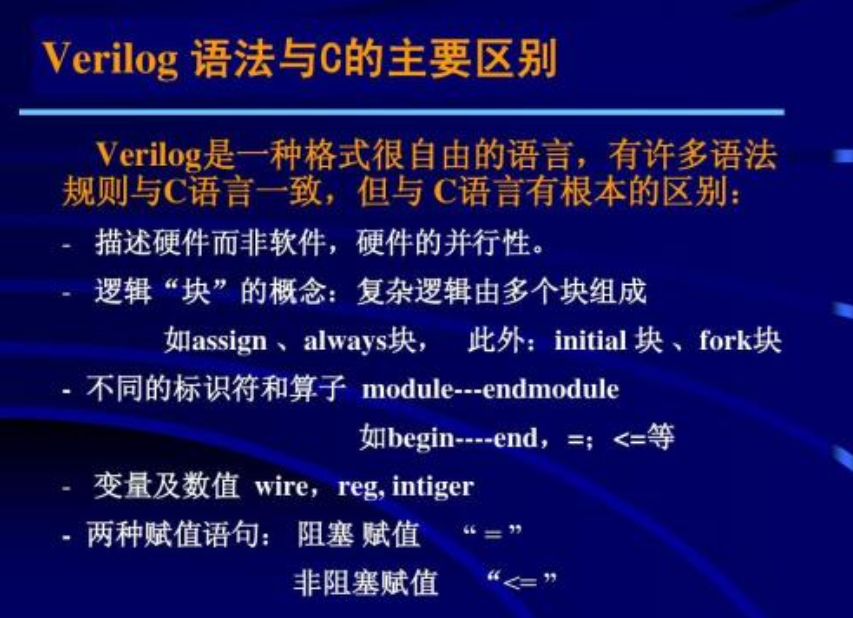

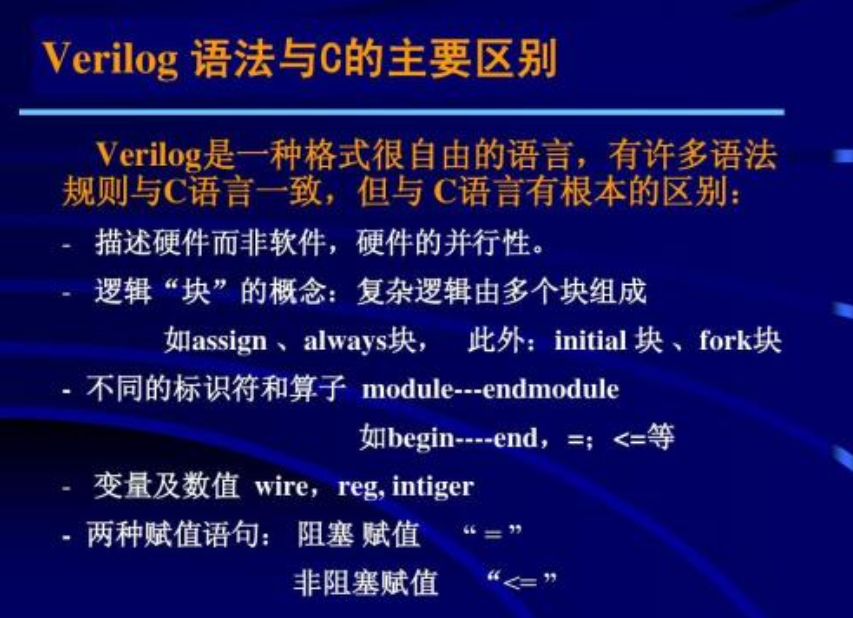

Verilog HDL的最大特点就是易学易用,如果有C语言的

编程

经验,可以在一个较短的时间内很快的学习和掌握,因而可以把Verilog HDL内容安排在与ASIC设计等相关课程内部进行讲授,由于HDL语言本身是专门面向硬件与系统设计的,这样的安排可以使学习者同时获得设计实际电路的经验。与之相比,VHDL的学习要困难一些。但Verilog HDL较自由的语法,也容易造成初学者犯一些错误,这一点要注意。

节通过硬件描述语言

Verilog

HDL对二十进制编码器的描述,介绍

Verilog

HDL程序的基本结构及特点。

2023-08-28 09:54:34

212

212

Verilog

规范对于一个好的IC设计至关重要。

2023-08-17 10:14:07

121

121

Verilog

大量例程(简单入门到提高)

2023-08-16 11:49:31

0

0

读者如果学习了

verilog

,并且有了一定的实践经验的话应该强烈的感受到,

verilog

和软件(诸如C/C++)有着本质且明显的差别,是一条不可跨越的鸿沟。

2023-06-28 10:44:32

118

118

Verilog

模块之间的连接是通过模块端口进行的。 为了给组成设计的各个模块定义端口,我们必须对期望的硬件设计有一个详细的认识。 不幸的是,在设计的早期,我们很难把握设计的细节。 而且,一旦模块

2023-06-12 10:05:01

266

266

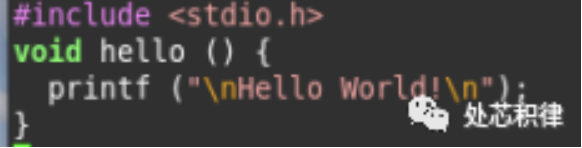

PLI全称 Program Language Interface,程序员可以通过PLI在

verilog

中调用C函数,这种访问是双向的。

2023-06-01 17:32:22

374

374

本文主要介绍

verilog

常用的循环语句,循环语句的

用途

,主要是可以多次执行相同的代码或逻辑。

2023-05-12 18:26:43

551

551

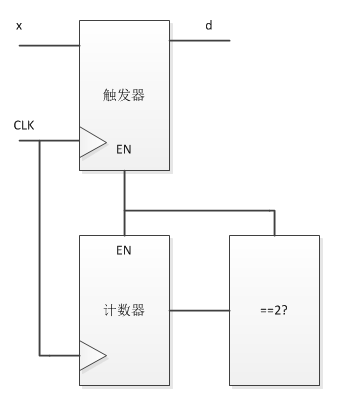

本文将从

Verilog

和边沿检测的基本概念入手,介绍

Verilog

边沿检测的原理和应用代码示例。

2023-05-12 17:05:56

1118

1118

fpga学习,

verilog

学习,

verilog

经典学习代码

2023-02-13 09:32:15

12

12

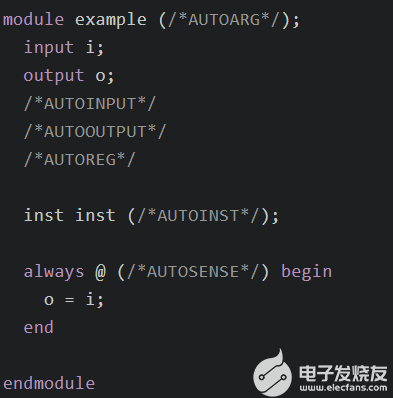

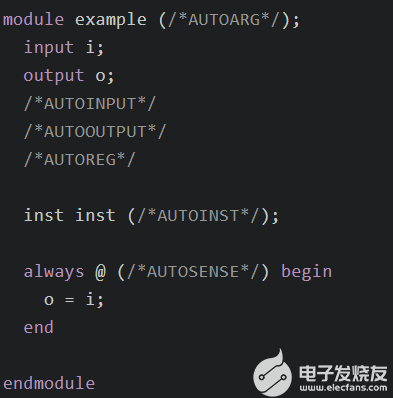

Verilog

-mode是由Michael McNamara mac@

verilog

.com和Wilson Snyder wsnyder@wsnyder.org编写。难能可贵的是,这个

verilog

-mode保持着每月都有更新。

2023-01-24 17:01:00

1145

1145

Verilog

HDL是一种用于数字系统设计的语言。用

Verilog

HDL描述的电路设计就是该电路的

Verilog

HDL模型也称为模块。

Verilog

HDL既是一种行为描述的语言也是一种结构描述的语言。

2022-12-08 14:00:57

1135

1135

第一句话是:还没学数电的先学数电。然后你可以选择

verilog

或者VHDL,有C语言基础的,建议选择VHDL。因为

verilog

太像C了,很容易混淆,最后你会发现,你花了大量时间去区分这两种语言,而

2022-11-03 09:02:56

1961

1961

写代码是给别人和多年后的自己看的。 关于

Verilog

代码设计的一些风格和方法之前也写过一些

Verilog

有什么奇技淫巧?

2022-10-24 15:23:54

708

708

在实际工作中,许多公司对

Verilog

程序编写规范都有要求。在公司内部统一

Verilog

程序编写规范不仅可以增强程序的可读性、可移植性,而且也有助于逻辑工程师之间交流、沟通,提升逻辑组成员之间的团队协作能力。本文就大部分公司常见的

Verilog

程序编写规范作一个介绍。

2022-09-15 09:35:58

2614

2614

Verilog

HDL(Hardware Description Language)是在

用途

最广泛的C语言的基础上发展起来的一种硬件描述语言,具有灵活性高、易学易用等特点。

Verilog

HDL可以在较短的时间内学习和掌握,目前已经在FPGA开发/IC设计领域占据绝对的领导地位。

2022-09-13 14:34:20

1018

1018

Verilog

-mode是由Michael McNamara mac@

verilog

.com和Wilson Snyder wsnyder@wsnyder.org编写。难能可贵的是,这个

verilog

-mode保持着每月都有更新。

2022-03-29 14:56:12

4162

4162

“ 本文主要分享了在

Verilog

设计过程中一些经验与知识点,主要包括

Verilog

仿真时常用的系统任务、双向端口的使用(inout)、边沿检测”

2022-03-15 13:34:56

1396

1396

Verilog

HDL入门教程-

Verilog

HDL的基本语法

2022-01-07 09:23:42

137

137

Verilog

HDL与VHDL是当前最流行的两种硬件设计语言,两者各有优劣,也各有相当多的拥护者,都通过了IEEE 标准。VHDL在北美及欧洲应用很普遍,

Verilog

HDL 语言在中国、日本

2021-11-06 09:05:57

15

15

Verilog

HDL入门教程.pdf

2021-11-02 16:27:14

93

93

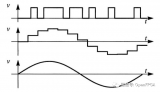

混合信号建模语言

Verilog

-AMS很多人做模拟电路的朋友,都希望有一款“模拟FPGA”,希望有一个“模拟的

Verilog

”,但现实是没有“模拟的

Verilog

”只有混合信号建模语言

2021-10-21 14:50:51

8219

8219

该FPGA项目旨在详细展示如何使用

Verilog

处理图像,从

Verilog

中读取输入位图图像(.bmp),处理并将处理结果写入

Verilog

中的输出位图图像。提供了用于读取图像、图像处理和写入图像

2021-09-23 15:50:21

4535

4535

FPGA CPLD中的

Verilog

设计小技巧(肇庆理士电源技术有限)-FPGA CPLD中的

Verilog

设计小技巧

2021-09-18 16:49:18

34

34

知乎上刷到一个问题,问性能最强的编程语言是什么?看到高赞回答到是

Verilog

,然后在评论区就引发了一场

Verilog

到底算不算编程语言的争论,我觉得比较有意思,所以就也打算唠唠这个事情。 趁着最近

2021-08-23 14:30:49

5126

5126

Verilog

入门教程,介绍

Verilog

的语法知识,基本程序编写。

2021-08-13 10:56:40

2

2

本文将介绍如何使用Icarus

Verilog

+GTKWave来进行

verilog

文件的编译和仿真。 Icarus

Verilog

Icarus

Verilog

极其小巧,支持全平台

2021-07-27 09:16:50

4020

4020

Verilog

HDL是一种以文本形式描述数字系统硬件的结构和行为的硬件描述语言,也可描述逻辑电路图、逻辑表达式等。

Verilog

HDL和VHDL是目前主流的、最受欢迎的两种硬件描述语言。

2021-07-23 14:36:55

8628

8628

1364-2001,即所谓的

Verilog

-2001。与过去的标准相比,它包含了很多扩展,克服了原来标准的缺点,并引入了一些新的语言

特征

。2005年,IEEE发布了1364-2005标准,称为Ve

2021-06-21 14:46:08

9212

9212

Verilog

数字系统设计教程(第2版)免费下载。

2021-05-12 14:26:37

71

71

简单介绍

Verilog

HDL语言和仿真工具。

2021-05-06 16:17:10

613

613

Verilog

语法进阶说明。

2021-05-06 16:14:58

29

29

本

Verilog

硬件描述语言参考手册是根据IEEE 的标准“

Verilog

硬件描述语言参考手册1364-1995”编写的。OVI (Open

Verilog

International) 根据

2021-02-05 16:24:00

72

72

Verilog

黄金参考指南是一个紧凑的快速参考指南

Verilog

硬件描述语言,其语法,语义,综合和应用程序的硬件设计。

2021-02-01 15:37:00

22

22

《基于

Verilog

语言的实用FPGA设计》中,K.科夫曼结合其工作实践,讲解了利用

Verilog

进行FPGA设计的方法和技巧。《基于

Verilog

语言的实用FPGA设计》内容涉及

Verilog

语言

2021-01-25 08:00:00

6

6

本文档的主要内容详细介绍的是

Verilog

教程之

Verilog

HDL程序设计语句和描述方式。

2020-12-09 11:24:23

44

44

学习内容:使用HDL设计的先进性,

Verilog

的主要

用途

,Ⅴerilog的历史如何从抽象级( levels of abstraction)理解,电路设计,Ⅴerilog描述

2020-10-29 17:30:37

26

26

本文主要阐述了

verilog

中端口的三种类型及

verilog

语言入门教程。

2020-08-27 09:29:28

9602

9602

今天给大家分享一个VHDL和

Verilog

的工具。很多新手初次学习FPGA都曾遇到过一个问题:是学

Verilog

OR VHDL?

2020-08-25 09:22:05

5596

5596

Verilog

HDL简称

Verilog

,它是使用最广泛的硬件描述语言。

2020-03-22 17:29:00

3564

3564

wire 和reg是

Verilog

程序里的常见的两种变量类型,他们都是构成

verilog

程序逻辑最基本的元素。正确掌握两者的使用方法是写好

verilog

程序的前提。

2020-03-08 17:18:00

10971

10971

硬件描述语言基本语法和实践

(1)VHDL 和

Verilog

HDL的各自特点和应用范围

(2)

Verilog

HDL基本结构语言要素与语法规则

(3)

Verilog

HDL组合逻辑语句结构

2019-07-03 17:36:00

51

51

Verilog

HDL是一种用于数字系统设计的语言。用

Verilog

HDL描述的电路设计就是该电路的

Verilog

HDL模型也称为模块。

Verilog

HDL既是一种行为描述的语言也是一种结构描述的语言。

2019-03-08 14:29:12

11704

11704

本文主要介绍了

Verilog

HDL 语言的一些基本知识,目的是使初学者能够迅速掌握HDL 设计方法,初步了解并掌握

Verilog

HDL语言的基本要素,能够读懂简单的设计代码并能够进行一些简单设计的

Verilog

HDL建模。

2019-02-11 08:00:00

91

91

本文档的主要内容详细介绍的是

Verilog

HDL教程之

Verilog

HDL的命令格式资料说明。

2019-01-09 08:00:00

31

31

本文档的主要内容详细介绍的是

Verilog

HDL入门教程之

Verilog

HDL数字系统设计教程。

2018-09-20 15:51:26

74

74

学习

verilog

最重要的不是语法,“因为10%的语法就能完成90%的工作”,

verilog

语言常用语言就是always@(),if~else,case,assign这几个了。

2018-03-26 14:06:00

2576

2576

Verilog

作为一种种硬件描述语言目前已经得到了普遍运用。本文主要介绍了

Verilog

特点、

Verilog

用途

以及

Verilog

实现74LS194芯片的程序介绍。

2017-12-22 17:26:08

6051

6051

华为的

verilog

编码规范

2017-11-01 08:41:26

37

37

verilog

2017-09-08 09:37:26

7

7

FPGA

verilog

相关设计实践

2017-09-06 11:19:34

32

32

本文主要介绍了

Verilog

HDL 语言的一些基本知识,目的是使初学者能够迅速掌握HDL设计方法,初步了解并掌握

Verilog

HDL语言的基本要素,能够读懂简单的设计代码并能够进行一些简单设计的

Verilog

HDL建模。

2016-07-15 15:27:00

13

13

Xilinx FPGA工程例子源码:

Verilog

编写的信道估计

2016-06-07 14:54:57

36

36

Verilog

HDL 华为入门教程

2016-06-03 16:57:53

45

45

verilog

通信系统设计,利用FPGA实现通信系统设计。

2016-05-31 16:08:58

17

17

Verilog

入门的实例代码,有需要的下来看看

2016-05-24 10:03:05

19

19

Verilog

_HDL语言的学习,为FPGA编程打下坚实的基础

2016-05-19 16:40:52

12

12

Verilog

_HDL教程,又需要的朋友下来看看

2016-05-11 17:30:15

16

16

Verilog

HDL程序设计教程-人邮

2016-05-11 11:30:19

32

32

本章介绍

Verilog

HDL的基本要素,包括标识符、注释、数值、编译程序指令、系统任务和系统函数。另外,本章还介绍了

Verilog

硬件描述语言中的两种数据类型。

verilog

相关教程材料,有兴趣的同学可以下载学习。

2016-04-25 16:09:32

16

16

verilog

代码规范,学会写代码还不行,我们需要更加的规范。

2016-03-25 14:28:34

35

35

适合

verilog

初学者的教程,可以好好参考学习。

2016-03-25 14:06:32

12

12

适合

verilog

初学者的教程,可以好好参考学习。

2016-03-25 14:03:14

11

11

适合

verilog

初学者的教程,可以好好参考学习。

2016-03-25 13:55:16

34

34

适合

verilog

初学者的教程,可以好好参考学习。

2016-03-25 13:45:54

17

17

verilog

_代码资料,非常实用的代码示例。

2016-02-18 15:00:10

33

33

verilog

语言开发的串口模块程序,测试可用。

2015-12-25 10:25:19

4

4

数字系统设计:

VERILOG

实现 (第2版)

2015-11-30 10:21:33

14

14

Quartus II Introduction Using

Verilog

Design

2015-11-24 11:42:20

6

6

Verilog

硬件描述语言参考手册,

Verilog

语法内容介绍

2015-11-12 17:20:37

11

11

verilog

verilog

verilog

verilog

verilog

verilog

verilog

verilog

2015-11-12 14:43:51

2

2

verilog

语言经典教材,本书讲解了

verilog

的基本语法和经典例子等等。

2015-11-10 11:44:20

23

23

Verilog

HDL语言的IEEE标准,2005年版

2015-11-06 16:52:27

58

58

Verilog

HDL程序设计与实践着重介绍了

Verilog

HDL语言

2015-10-29 14:45:47

19

19

The

Verilog

Hardware Description Language

2013-09-09 17:38:37

33

33

本资料是关于夏宇闻老师优秀的

verilog

教程课件,其中包括

verilog

讲稿PPT、

verilog

课件、

verilog

例题等。

2012-09-27 15:00:49

468

468

本文简单讨论并总结了VHDL、

Verilog

,System

verilog

这三中语言的各自特点和区别 As the number of enhancements

2012-01-17 11:32:02

149

149

Verilog

黄金参考指南是

Verilog

硬件描述语言及其语法语义合并以及将它应用到硬件设计的一个简明的快速参考指南

Verilog

黄金参考指南并不是要代替IEEE 的标准

Verilog

语言参考手册它不像

2011-12-26 15:03:06

145

145

《

Verilog

HDL 程序设计教程》对

Verilog

HDL程序设计作了系统全面的介绍,以可综合的设计为重点,同时对仿真和模拟也作了深入的阐述。《

Verilog

HDL 程序设计教程》以

Verilog

-1995标准为基础

2011-09-22 15:53:36

717

717

本教程讲解了如何利用

VERILOG

硬件描述语言来设计和验证一个复杂的数字系统的方法。下面就复杂数字系统的概念、

用途

和几个有关的基本问题做一些说明

2011-05-09 17:01:37

156

156

Synthesizable

Verilog

is a subset of the full

Verilog

HDL [9] that lies within the domain

2011-03-03 15:46:01

279

279

Verilog

HDL练习题

2010-11-03 16:47:13

193

193

Verilog

-A

2010-08-22 12:54:40

24

24

FFT

Verilog

RTL

2010-07-08 15:55:21

41

41

卡内基梅陇大学

verilog

课程讲义

This is not one cohesive presentation on

Verilog

.

2010-04-15 14:10:15

69

69

Verilog

HDL入门教程(华为绝密资料)

本文主要介绍了

Verilog

HDL 语言的一些基本知识,目的是使初学者能够迅速掌握HDL设计方法,初步了解并掌握

Verilog

HDL语言的

2010-04-02 11:52:21

2136

2136

Verilog

HDL 华为入门教程

本文主要介绍了

Verilog

HDL 语言的一些基本知识,目的是使初学者能够迅速掌握HDL设计方法,初步了解并掌握

Verilog

HDL语言的基本要素,能

2010-02-11 08:35:38

139

139

VHDL和

Verilog

HDL语言对比

Verilog

HDL和VHDL都是用于逻辑设计的硬件描述语言,并且都已成为IEEE标准。VHDL是在1987年成为IEEE标准,

Verilog

HDL

2010-02-09 09:01:17

10162

10162

Verilog

HDL语言简介

1.什么是

Verilog

HDLVerilog HDL是硬件描述语言的一种,用于数

2010-02-09 08:59:33

3258

3258

Verilog

HDL程序基本结构与程序入门

Verilog

HDL程序基本结构

Verilog

HDL是一种用于数字逻辑电路设计的语言。用

Verilog

HDL描述的

2010-02-08 11:43:30

2083

2083

Verilog

-HDL实践与应用系统设计本书从实用的角度介绍了硬件描述语言

Verilog

-HDL。通过动手实践,体验

Verilog

-HDL的语法结构、功能等内涵。在前五章,以简单的实例列举了

Verilog

-HDL的用法;

2009-11-14 22:57:40

139

139

Verilog

典型电路设计

2009-08-03 09:23:57

60

60

This book is on the IEEE Standard Hardware Description Languagebased on the

Verilog

® Hardware

2009-07-23 09:01:32

187

187

This book is on the IEEE Standard Hardware Description Languagebased on the

Verilog

® Hardware

2009-07-23 08:59:50

30

30

The

Verilog

Programming Language Interface, commonly called the

Verilog

PLI,is one of the more

2009-07-22 09:57:33

10

10

The

Verilog

Programming Language Interface, commonly called the

Verilog

PLI,is one of the more

2009-07-22 09:55:36

83

83

Verilog

HDL 综合实用教程第1章 基础知识第2章 从

Verilog

结构到逻辑门第3章 建模示例第4章 模型的优化第5章 验证附录A 可综合的语言结构附录B 通用库

2009-07-20 11:21:13

86

86

(This introduction is not part of IEEE Std 1364-2001, IEEE Standard

Verilog

® Hardware

2009-07-18 11:02:12

195

195

(This introduction is not part of IEEE Std 1364-2001, IEEE Standard

Verilog

® Hardware

2009-07-18 10:58:28

44

44

什么是

Verilog

HDL?

Verilog

HDL是一种硬件描述语言,用于从算法级、门级到开关级的多种抽象设计层次的数字系统建模。被建模的数字系统

2009-01-18 14:53:26

3435

3435

IEEE Standard

Verilog

Hardware Description Language

(This introduction is not part of IEEE Std

2008-10-21 15:37:44

0

0

已全部加载完成