注意,拨码开关向上板为NO向下板为OFF,大家可以从图中看出,当SW3为NO、SW4为NO、SW5为OFF、SW6为OFF时,灯D3亮,与我们的真值表相符。说明该程序成功。下面两张图同理。

可以和真值表对比。实际操作与我们想要实现的功能一样。

可以和真值表对比。实际操作与我们想要实现的功能一样。

https://www.diangon.com/wenku/rd/dianzi/201505/00023654.html

https://blog.csdn.net/weixin_41445387/article/details/82998004

一、3-8译码器简介1、简介译码是编码的逆过程。其功能是将具有特定含义的二进制码进行辨别,并转换成控制信号,具有译码功能的逻辑电路称为译码器。如果有n个二进制选择线,则最多可译码转换成2n个数据。2、功能:将输入的3位2进制数翻译成10进制的8位输出。3-8译码器输入是二进制。3只脚也就是3位二进制数。输入可以3位二进制数。3位二进制最大是111 也就是8。3-8译码器输出是8个脚,表示10进制。是根据输入的二进制数输出。如果输入是101 那么就是第5只脚高电平,表示二进制数是5。3-8

本关任务:在Logisim中,利用上一关中设计的2-4译码器级联来构建3-8译码器,使能信号Enable高电平有效。

译码器(Decoder)能将二进制代码的特定含义翻译出来,是一类多输入多输出组合逻辑器件,其可以分为:变量译码和显示译码两类。 变量译码器一般是一种较少输入变为较多输出的器件,常见的有n线-2^n线译码和BCD码译码两类;显示译码器用来将二进制数转换成对应的七段码,一般其可分为驱动LED和驱动LCD两类。

计算机中通常有地址译码器、指令译码器等。

利用2-4译码器级联扩展构建3-8

一、组合逻辑电路与时序逻辑电路

组合逻辑电路:任意时刻的输出仅仅由该时刻的输入决定,与电路当前的状态无关。

时序逻辑电路:任意时刻的输出不仅由该时刻的输入决定,还与电路当前的状态有关。

二、38译码器的工作原理

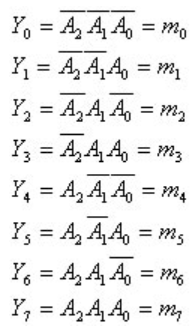

表①、38译码器真值表

3种输入状态翻译成8种输出状态。

三、Verilog代码实现

module decoder_38 (

a,b,c,data

input wire a;

input wire b;

input wire c;

output reg

output reg [7:0]out;

always @(a,b,c)begin //当a,b,c信号变化时,always语句触发

case({a,b,c}) //位拼接 {}

3'b000: out = 8'b0000_0001;

3'b001: out = 8'b0000_001

2.实验原理不太清楚:课下要好好看看原理。

3.文件名必须与VHDL文件中的设计实体名保持一致。

4.思考软件仿真时输入信号应如何设置?: 在修改时钟信号的地方,可选时间和频率选项,而频率的选项在时间下面,容易忽视,选完频率后,就可以继续设置了。

5.在设置引脚时,一定要看电路板,以及电路图,找对各个输入输出接口对应的芯片引脚。

用Verilog设计一个3-8译码器,要求分别使用if-elsecase语句。输入端分别为三个拨码开关,确认键为按钮,其中三个为3-8译码器的输入,另一个为确认键,先按输入,再按下确认键,开始译码。

(1)学习并掌握Quartus II的使用方法

(2)学习使用原理图方法进行逻辑设计输入,并初步了解可编程器件设计的全过程

(3)熟悉ALTERA公司EDA设计工具软件Quartusll设计一个3-8译码器,并在实验开发系统上熟悉原理图输入及仿真步骤,掌握组合逻辑电路的设计及静态测试方法

二、实验仪器设备

(1) PC机一台。

(2)Quartus Ⅱ开发软件一套

(3)EDA实验开发系统一套

三、实验原理

译码是相对于编码的逆过程,在基于一定硬件支持下能是将

可以和真值表对比。实际操作与我们想要实现的功能一样。

可以和真值表对比。实际操作与我们想要实现的功能一样。